虽然台积电3nm芯片已经量产,但截止昨天,我们都没有看到芯片公司发布相关产品。到了今天,这个局面终于被打破了。

美国芯片公司Marvell表示,公司基于台积电 3 纳米 (3nm) 工艺打造的数据中心芯片正式发布。

据Marvell介绍,公司在该节点中的业界首创硅构建模块包括 112G XSR SerDes(串行器/解串行器)、Long Reach SerDes、PCIe Gen 6 / CXL 3.0 SerDes 和 240 Tbps 并行芯片到芯片互连。

按照Marvell所说,SerDes 和并行互连在芯片中充当高速通道,用于在chiplet内部的芯片或硅组件之间交换数据。与 2.5D 和 3D 封装一起,这些技术将消除系统级瓶颈,以推进最复杂的半导体设计。

SerDes 还有助于减少引脚、走线和电路板空间,从而降低成本。超大规模数据中心的机架可能包含数以万计的 SerDes 链路。

根据他们提供的数据,新的并行芯片到芯片互连可实现高达 240 Tbps 的聚合数据传输,比多芯片封装应用的可用替代方案快 45%。

换句话说,互连传输速率相当于每秒下载 10,000 部高清电影,尽管距离只有几毫米或更短。

Marvell 将其 SerDes 和互连技术整合到其旗舰硅解决方案中,包括Teralynx开关_,PAM4和相干DSP,Alaska 以太网物理层 (PHY)设备,OCTEON处理器_,Bravera存储控制器,Brightlane汽车以太网芯片组和定制 ASIC。

而转向 3nm 工艺使工程师能够降低芯片和计算系统的成本和功耗,同时保持信号完整性和性能。

3nm,台积电的新里程碑

据台积电介绍,公司的3奈米(N3)制程技术将是5奈米(N5)制程技术之后的另一个全世代制程,在N3制程技术推出时将会是业界最先进的制程技术,具备最佳的PPA及电晶体技术。

相较于N5制程技术,N3制程技术的逻辑密度将增加约70%,在相同功耗下速度提升10-15%,或者在相同速度下功耗降低25-30%。

不过,N3 的工艺窗口(产生定义结果的参数范围)相对较窄,就产量而言可能并不适合所有应用。而且,随着制造工艺变得越来越复杂,它们的寻路、研究和开发时间也越来越长,所以我们不再看到台积电和其他代工厂每两年出现一个全新的节点。

对于 N3,台积电的新节点导入周期将延长至 2.5 年左右。这意味着台积电将需要提供 N3 的增强版本,以满足其客户的需求,这些客户仍在寻求每瓦性能的改进以及每年左右晶体管密度的提升。

在2022 年技术研讨会上,台积电也讨论了四种 N3 衍生制造工艺(总共五个 3 纳米级节点)——N3E、N3P、N3S 和 N3X——这都将在未来几年推出。

这些 N3 变体旨在为超高性能应用提供改进的工艺窗口、更高的性能、更高的晶体管密度和增强的电压。

其中N3E 提高了性能,降低了功耗,并增加了工艺窗口,从而提高了亮了。但代价是该节点的逻辑密度略有降低。

与 N5 相比,N3E 的功耗将降低 34%(在相同的速度和复杂度下)或 18% 的性能提升(在相同的功率和复杂度下),并将逻辑晶体管密度提高 1.6 倍。

根据报道,台积电将在 2024 年左右的某个时候推出 N3P(其制造工艺的性能增强版本)以及 N3S(该节点的密度增强版本)。

但台积电目前并未透露这些变体的更多信息。对于那些无论功耗和成本都需要超高性能的客户,台积电将提供N3X,本质上是N4X的思想继承者。同样,台积电没有透露有关该节点的详细信息,只是说它将支持高驱动电流和电压。

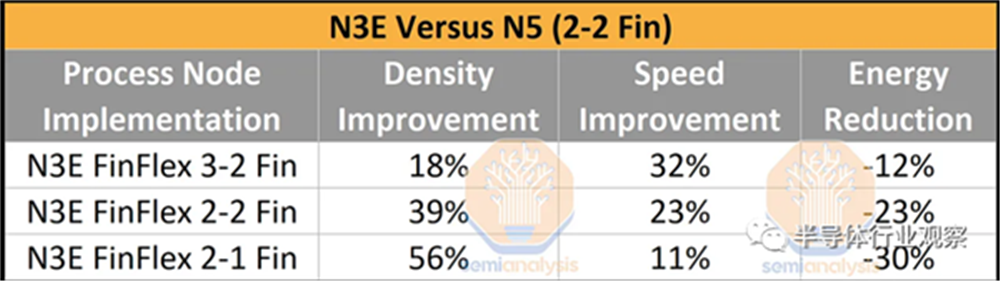

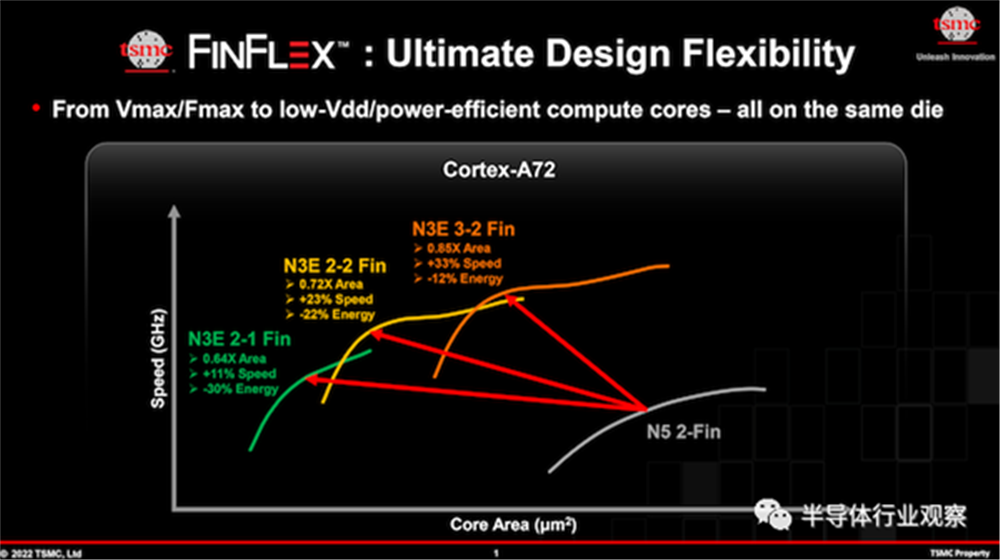

值得一提的是,台积电所有这些技术都将支持 FinFlex,这是台积电的一项“秘方”功能,可大大提高设计灵活性,并允许芯片设计人员精确优化性能、功耗和成本。简而言之,FinFlex 允许芯片设计人员精确定制他们的构建模块,以实现更高的性能、更高的密度和更低的功耗。

在实际应用中,台积电的 FinFlex 技术将允许芯片设计人员在一个块内混合和匹配不同类型的标准单元,以精确定制性能、功耗和面积。对于像 CPU 核心这样的复杂结构,这种优化提供了很多机会来提高核心性能,同时仍然优化芯片尺寸。

但是,我们必须强调的是,FinFlex 不能替代节点专业化(性能、密度、电压),因为工艺技术比单一工艺技术中的库或晶体管结构有更大的差异,但 FinFlex 看起来是优化性能、功率和成本的好方法台积电的N3节点。最终,这项技术将使基于 FinFET 的节点的灵活性更接近于基于纳米片/GAAFET 的节点,这些节点将提供可调节的通道宽度以获得更高的性能或降低功耗。

三星3nm,起了个大早

其实早在台积电公布3nm量产之前,三星早就宣布已经实现了3nm工艺的量产。

2022年六月,三星宣布已开始了采用环栅 (GAA) 晶体管架构的 3 纳米 (nm) 工艺节点的初始生产。

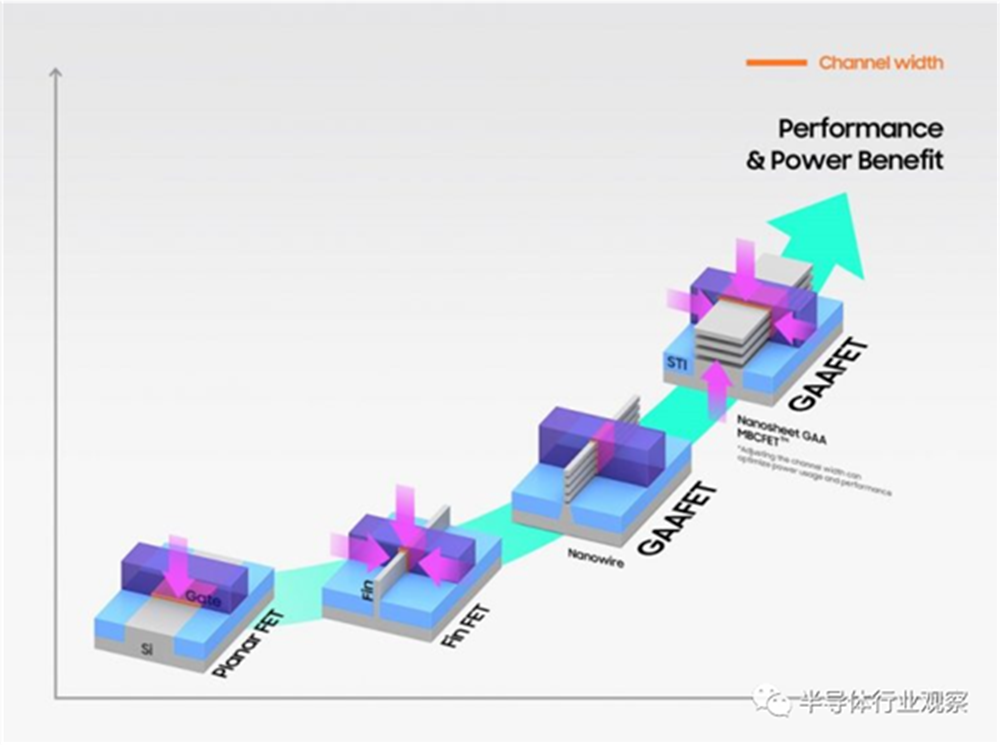

其中用到的多桥通道 FET (MBCFET ) 是三星首次采用的 GAA 技术,该工艺突破了 FinFET 的性能限制,通过降低电源电压水平提高功率效率,同时还通过增加驱动电流能力提高性能。

该公司也正在开始将纳米片晶体管与半导体芯片一起用于高性能、低功耗计算应用,并计划扩展到移动处理器。

三星表示,借助公司专有技术利用具有更宽通道的纳米片,与使用具有更窄通道的纳米线的 GAA 技术相比,可实现更高的性能和更高的能效。

利用 3nm GAA 技术,三星将能够调整纳米片的通道宽度,以优化功耗和性能,以满足各种客户需求。

此外,GAA 的设计灵活性非常有利于设计技术协同优化 (DTCO),这有助于提高功率、性能、面积 (PPA) 优势。

与5nm工艺相比,第一代3nm工艺相比5nm功耗最高可降低45%,性能提升23%,面积减少16%,而第二代3nm工艺则功耗最高可降低50%,性能提高 30%,面积减少 35%。

如上所述,和台积电的工艺不一样,三星3nm采用了GAA晶体管,这开启了一个新时代。

自 2019 年他们最初宣布该技术以来,三星一直致力于 3nm/GAAFET 技术的研发。三星特有的 GAA 晶体管技术是多桥通道 FET (MBCFET),这是一种基于纳米片的实现。

基于纳米片的 FET 高度可定制,纳米片的宽度是定义功率和性能特征的关键指标:宽度越大,性能越好(在更高功率下)。因此,专注于低功耗的晶体管设计可以使用更小的纳米片,而需要更高性能的逻辑可以使用更宽的纳米片。

在三星3nm被发布早期,业内人士一直在诟病其良率,但据业内人士在今年一月透露,三星电子公司周一大幅提高了其为无晶圆厂客户生产的业界最先进的 3 纳米芯片的良率。

知情人士表示,三星的第一代 3 纳米工艺节点的生产良率达到了“完美水平”,但他没有进一步详细说明。

而在此前,台湾媒体报道称,台积电的3纳米工艺生产良率高达85%,高于三星。但韩国业内消息人士淡化了这份报告,称这个数字似乎被夸大了。

他们表示,考虑到台积电向苹果提供业界最小芯片的量产和交付时间表,其生产良率最多为50%。

按照媒体所说,因为在第一代3nm上折戟,三星正在大力投入到第二代工艺的研发中。

报告披露,三星第二代3nm GAA 工艺将会在2024年量产,工艺将加入MBCFET 架构,性能也将提升不少。

虽然三星并没有分享4nm 节点的统计差异,但与该公司5nm 工艺相比,第二代3nm GAA 仍有望降低多达50% 的功耗、提升30% 性能、以及减少35% 的晶片面积占用。

巨头会师2纳米,决战

虽然三星和台积电都在3nm上花了不少心思,但从过去的新闻和厂商的公告可以看到,似乎大家都对第一代的3nm工艺不感兴趣。例如市场上一度传言,苹果会成为台积电第一代3nm工艺的唯一客户。不过,这家美国巨头迄今都没有公布其3nm产品。

由此可见,第一代3nm不被看好是业界共识了。但市场对工艺的追逐从目前看来,尚未停止。除了这两家晶圆代工厂以外,据报道,英特尔也将在2023年年底推出其 3nm 工艺节点。而他们似乎也把目光定在了2nm。

届时,英特尔的Intel 20A(2nm)将迎来Angstrom时代,利用GAA(RibbonFET)晶体管和PowerVia技术提高功率保持能力。

英特尔的竞争对手台积电将在 2025 年采用其2nm 节点的 GAA ,在芯片制造商遇到小型化极限时让前者领先一步。再加上将于2025 年实现 2 纳米原型线的日本新创企业Rapidus 和三星。

对芯片公司而言,如何面对芯片设计挑战和成本挑战,会是未来他们未来多年的头等大事。